台積電:EDA工具需要新典範

台積電設計暨技術平台副總經理侯永清在年度ISSCC演說中表示,工程師需要能因應今日晶片設計複雜性的新工具。

在近日於美國舉行之年度國際固態電路會議(International Solid State Circuits Conference,ISSCC)的一場專題演說中,台積電設計暨技術平台副總經理侯永清(Cliff Hou)表示,工程師需要能因應今日晶片設計複雜性的新工具;而他也指出,針對四個目前的主要市場,需要採用包括機器學習在內之新技術、新假設的個別工具。

「我們需要一種新的設計典範(paradigm)來克服晶片設計挑戰;」侯永清指出:「我們是時候該推進設計典範,我們一直只涵蓋設計領域的一小部份。」他表示,產業界在過去十年是由行動應用所驅動,圍繞著智慧型手機SoC建立設計資料庫:「現在我們了解,行動應用可以做為一個起點,但我們需要為汽車、高性能系統以及物聯網(IoT)等設計考量大不相同的應用,最佳化電路設計。」

侯永清展示了台積電針對一系列手機與可穿戴式裝置設計應用的四種不同SRAM設計,他也在專題演說中列出台積電已經看到某些進展的棘手挑戰;舉例來說,從40奈米到7奈米節點,金屬層的電阻增加一倍,而台積電已經在導線下打造了複雜的通孔柱(via pillars)堆疊,但並不能完全減輕這個問題。

台積電還根據晶片是否需要更高的密度或速度,採用了兩種金屬;侯永清表示,那些選項:「需要設計變革以及EDA強化…EDA供應商們已經意識到這些問題,初步解決方案看來頗具前景。」此外,電源網路的建構也必須非常小心,以避免在電晶體密度增加時的單元利用率(cell utilization)下降;他描述了能讓單元利用率在7奈米節點由大約74%回升到79%的進展。

「當你設計電源網路時,得考量它們對電路設計的影響,並為其最佳化佈線,否則就無法獲得所有製程微縮的優勢;」侯永清還展示了能因應隨著設計轉移到更低電壓供電水準而增加之延遲變異(delay variation)的新技術,他並呼籲催生精細度更高的新一代設計編譯器,以最佳化特定領域與性能需求。

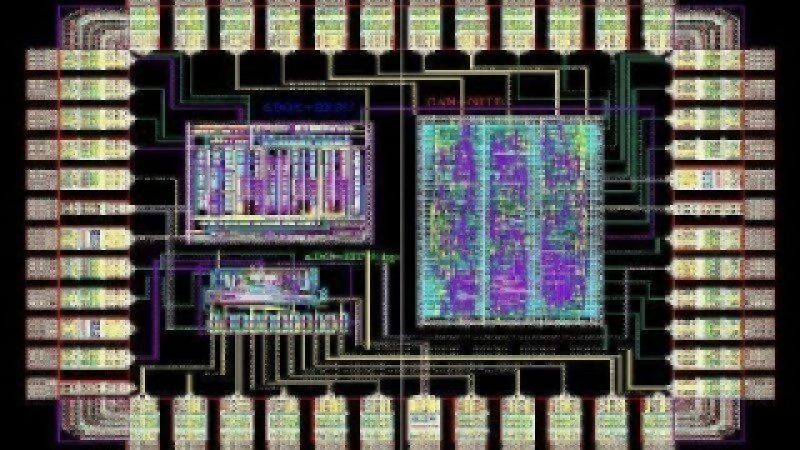

![[20170208 TSMC NT02P1]](/wp-content/uploads/sites/5/2020/04/20170208_TSMC_NT02P1.jpg)

台積電利用機器學習在晶片設計繞線前預測線路擁擠,讓速度增加了40MHz

(來源:ISSCC)

最後他展示了兩個將機器學習應用於晶片設計的案例,其中之一是在晶片佈線之前,運用預測線路擁擠(congestion)的模型,將晶片速度提升40MHz。另一個案例則是能產生2萬個時脈閘控單元(clock gating cell)的先進設計,因為規模太大,設計工程師會被迫採取全局約束(global constraint);侯永清展示了一個機器學習模型,能預測單元中的延遲並設定其個別限制。

編譯:Judith Cheng

(參考原文: TSMC Calls for New EDA Paradigm,by Rick Merritt)

訂閱EETimes Taiwan電子報

加入我們官方帳號LINE@,最新消息一手掌握!