是時候改善您的時脈了!

智慧連網裝置的出現對於時脈性能提出了更高的要求。本文解釋設計人員如何在因應這些挑戰的同時降低技術風險、縮短設計時間以及削減物料清單(BOM)。我們著眼於採用石英和基於MEMS技術的石英、石英晶體振盪器(XO)和高度整合的時脈解決方案。

幾乎每個電子元件都需要一個時脈源。例如,微控制器(MCU)使用振盪器,以便前進到下一條指令,無線電則需要精確的振盪器,才能將射頻(RF)訊號混合到基頻中加以處理。

智慧連網裝置的出現對於時脈性能提出了更高的要求。本文解釋設計人員如何在因應這些挑戰的同時降低技術風險、縮短設計時間以及削減物料成本清單(BOM)。我們著眼於採用石英和基於MEMS技術的石英、石英晶體振盪器(XO)和高度整合的時脈解決方案。

智慧連網裝置需要複雜的時脈樹

MCU通常包括用於非精確運算應用的內部電阻電容(RC)相移振盪器。這些振盪器使用整合的電阻-電容配對,以建立控制振盪器頻率的時間常數。此類振盪器具有大約1%的精準度並且表現出高抖動(在時脈轉換的時序中出現意外的隨機波動)。它們適用於不注重轉換時序的應用,例如為運算用MCU提供時脈以及驅動一個簡單的七段數位液晶顯示器(LCD)。這種顯示器需要多個時脈波形,但轉換時序容差為幾毫秒(ms)。此外,也可實現高達幾Mbps的UART通訊,這種情況下的時序容差約為幾百奈秒(ns),但這同時也代表著簡單RC振盪器的限值。

智慧連網產品透過藍牙(Bluetooth)、有線乙太網路、Wi-Fi或其他連線協定與雲端進行網路通訊。由於涉及無線電和/或高速資料,因此需要精確度達百萬分之一(ppm)的低抖動精確時脈。

產生精確時脈所需的關鍵因素是穩定的參考頻率,而這需要使用諧振器。諧振器是一種被動電子元件,在某些(諧振)頻率下自然振盪的振幅高於其他頻率——小提琴的琴弦就是一個簡單的例子。電子元件通常選用石英晶體和MEMS諧振器。諧振器的要求如下:

- 諧振頻率隨時間和溫度變化呈穩定態勢。如此可以避免時脈頻率漂移。

- 高品質因���(Q),確保諧振器只回應很窄的頻率範圍。

- 能夠在高訊號強度下操作,從而在輸出端達到良好的訊號雜訊比(SNR)。

第二項和第三項對於確保低抖動時脈訊號至關重要,可實現穩定的時序轉換。

由於諧振器是一種被動元件,因此需要可控制的能量來維持振盪並產生參考頻率。將諧振器以回饋配置耦合到維持放大器,即可實現這種穩定的振盪。如果石英晶體或MEMS諧振器搭配合適放大器,將會非常適合作為10Mbps及其上域值的資料傳輸之頻率參考。

石英諧振器具有高Q值和高輸出能力,適用於極低抖動的應用,它可以實現100飛秒(fs)的相位雜訊(以傳統的12kHz至20MHz頻寬測量)。MEMS諧振器能夠以非常穩定的頻率在擴展的溫度範圍內作業,而且兼具極高的可靠性,以及抗衝擊和振動性能,並能夠實現超小型時脈解決方案(接近1平方毫米)。MEMS諧振器具有較高的Q值和較低的輸出;可實現500fs的相位雜訊,而近期的諧振器設計也在不斷降低該值。例如,許多現代網路應用(例如PCIe)都支援較小的整合頻寬,因此這兩種技術都非常合適。

在嵌入式系統中建置時脈

在嵌入式系統中,可透過三種常見的諧振器建置來產生時脈訊號。

- 將石英晶體直接連接到「目標SoC」(由時脈驅動)

- 透過石英晶體振盪器或XO,為整個系統創建一個時脈輸出

- 基於石英或MEMS的時脈產生器,以低頻和高頻(>50MHz)創建一個或多個時脈輸出)

建置1:將晶體連接到目標SoC

在這種情況下,系統級晶片(SoC)設計配有持續放大器且可以直接連接晶體,通常使用電容來安排正確的反饋並調整頻率。SoC可根據需求放大參考時脈並可對其進行頻率轉換。圖1顯示直接連接至MCU的高頻和低頻晶體原理圖。

圖1:兩個晶體振盪器直接連接到MCU,顯示負載電容和串聯電阻

對於系統而言,只需以這種方式連接一個或兩個晶體即具有成本效益;電路板(PCB)的佈局也非常簡單,將晶體緊挨著SoC放置即可,這樣通常就能夠避免訊號完整性和電磁干擾(EMI)問題。

但是,有一些注意事項需要考慮:

- 晶體必須仔細挑選,以便相容於SoC的內部維持放大器電路。如果晶體的等效串聯電阻較放大器的負電阻更高,則振盪器可能無法啟動。

- 晶體可能需要負載電容以確保反饋相位正確,並且準確地設置頻率。

- 石英晶體具有相對較大的溫度係數。如果應用要求在-40°C至70°C範圍之外作業,可能需要使用溫度補償晶體振盪器(TCXO)或整合型MEMS時脈。

- 在基礎波形模式下作業的標準石英晶體之共振頻率等於或低於50MHz。在諧波模式下作業且頻率大於50MHz的石英晶體往往更昂貴。

建置2:晶體振盪器

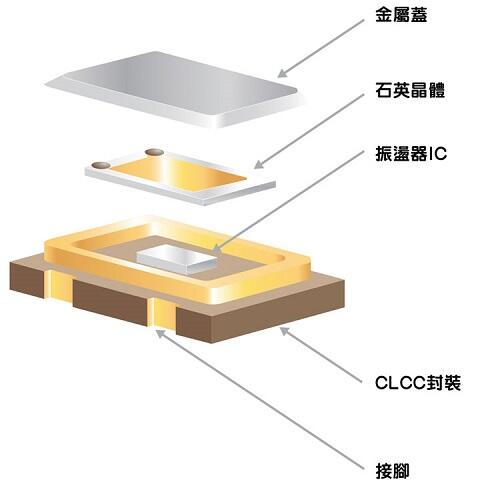

在單個封裝中整合的晶體和維持放大器稱為晶體振盪器(XO)。圖2所示為如何在密封組裝中將晶片與振盪器ASIC相結合。這種預封裝式解決方案雖然比單一晶體更為昂貴,但避免了上述注意事項1和2的連接問題,因而能夠保證啟動的可靠性以及輸出頻率的正確性。

圖2:晶振由石英晶片組成,傳統上採用陶瓷封裝並帶有金屬蓋

同樣地,需要一個或兩個XO的系統也極具成本效益。如果需要多種頻率、額外的緩衝輸出或高於50MHz的頻率,則系統可以從整合時脈產生器受益。

建置3:時脈產生器

在單個封裝中,高度整合的時脈產生器包含以下部份或全部功能:

- 諧振器,如石英或MEMS諧振器

- 維持放大器

- 鎖相環(PLL),用於透過倍頻實現一個或多個頻率,通常在1MHz~1GHz範圍內

- 一個或多個緩衝器,提供相同時脈頻率的多個副本

圖3顯示整合所有功能的原理圖

圖3:整合時脈產生器結合MEMS(或晶體)諧振器與振盪器,並透過可編程的PLL和緩衝輸出級擴展功能

圖4所示的時脈產生器採用模壓塑料QFN封裝,內含整合晶體和整合ASIC(包括維持放大器、PLL、兩個可編程分頻器和五個輸出緩衝器)。一次性可編程(OTP)的ROM儲存自訂配置(如頻率和輸出協定)。該設計並非採用晶片與ASIC共用密封封裝的傳統石英XO方案,而是讓完全組裝的密封封裝晶體與ASIC共用更低成本的塑料外殼。採用單獨封裝的晶體能與ASIC和基板隔離,除了保持清潔完好狀態,同時避免了石英表面附著任何污染物,從而在長時間的使用過程中表現出非常優異的頻率穩定性(也稱為「優異的老化性能」)。

時脈產生器的優勢

如果晶體或XO解決方案只需要一個或兩個頻率以及一個時脈訊號的單一副本,將會極具成本效益,更複雜的系統也能因為使用一個時脈產生器而獲益。

最顯著的優勢之一是減少系統元件數和削減整體BOM。圖5所示為需要多個時脈(高於和低於50 MHz頻率)的10 Gigabit乙太網路開關。多個XO、一個PLL和緩衝器的組合可以採用一個時脈產生器(如SM803,需要一個外部晶體)和一個整合MEMS諧振器的DSC400所取代。

圖4:5輸出時脈產生器方塊圖以及晶片安裝在基板上的照片(將組裝密封於塑料封裝之前)

圖5:10GbE開關顯示如何使用兩個時脈產生器取代一個複雜的12元件時脈樹

此外,整合時脈解決方案非常靈活,可透過編程OTP ROM來選擇不同的頻率和輸出協定。有時,所包含的I2C或SPI輸入或硬體接腳控制允許設計人員在嵌入式系統中安裝時脈後調整頻率。這對於具有可選設置的系統特別有用,而且還可以用於系統餘裕調整——特別是在特殊情況下加速時脈以獲得最佳性能。

最近,一家汽車製造商向我諮詢了一個EMI問題:用於操作環繞立體視覺攝影機的可編程時脈產生器在快速轉換時,產生了干擾汽車FM收音機的諧波。然而,我們的時脈產生器現已具備可變輸出上升/下降轉換時間的功能,客戶只需使用重新編程的新產品版本,即可免於支付昂貴的檢查或硬體更換費用。由於時脈設計提供的靈活性,從而避免了產品的延期和成本超支。

目前,時脈產生器常用的一項重要功能是「擴展」輸出時脈的功能(使用擴頻)。擴頻應用精心設計的時脈輸出頻率調變,其作用較小,不至於影響終端系統性能,但足以將固定時脈輸出的尖峰頻譜峰值擴展到更低幾個分貝的窄頻段中。降低峰值頻譜級,有助於防止EMI問題。擴頻和非擴頻時脈訊號的頻譜如圖6所示。

*圖6:透過調變時脈訊號和降低能量峰值(擴頻調變),就能夠降低EMI *

時脈產生器還可以顯著提高性能。使用單個振盪器並搭配緩衝器和鎖相環可產生多個時脈輸出,但這種「離散」方案需要在PCB上佈設多條時脈走線。這些走線容易受到串擾和反射影響;相形之下,從時脈產生器接腳輸出的多個時脈訊號則是乾淨的,而且具有較低的相對偏移以及匹配的上升/下降時間。因此,對於一個複雜的時脈樹而言,使用時脈產生器可在產生乾淨時脈的同時降低技術風險、縮短設計階段並減小電路板空間。

曾經將晶體放置在SoC旁邊的設計人員可能會擔心從中央時脈產生器佈設較長走線的問題以及可能發生訊號衰減和EMI。但是,如果操作得當,透過精心設計傳輸線路,合理端接和正確應用PCB層疊,集中式時脈解決方案能夠避免這些問題並節省成本。

採用時脈產生器,可將多個元件替換為預先設計的已封裝時脈產生器,能夠實現超大規模量產,達到嚴格的可靠性和品質標準。這不僅能夠確保為整個系統提高可靠性和降低總擁有成本(TCO), 還能夠盡可能地降低現場退修率。

架構時脈樹

當開始架構時脈樹時,全面瞭解整個終端系統十分重要。圖7介紹這種整體方法,並顯示可用的元件選項。還必須問問自己一些以下的問題類型:需要多少種不同的頻率?每一種頻率需要多少個副本?

圖7:所需的全部時脈訊號示例清單

考慮哪些頻率需要同步。圖5中的乙太網路交開關是自由運行時脈樹的一個示例。獨立的資料通道不需要同步進行時脈驅動。當資料流程的延遲可以透過緩衝進行管理時,以不同的時脈速率處理的單個資料通道也是一種自由運行或獨立進行時脈驅動的系統。

如果一個系統使用單個精密時脈,並透過嚴格控制的相位鎖定複製到多個位置,則這是一個同步系統。這種設計在高速資料傳輸中很常見,其中的低延遲是關鍵。對於這些系統,通常有兩個附加元件。

首先是一個抖動阻滯器,即一個帶有窄頻迴路濾波器的整合PLL。它並不會產生時脈訊號,而是用於消除現有時脈的抖動。另外,低附加抖動緩衝器能夠產生現有時脈的多個副本。

圖8所示為一個同步時脈系統。

*圖8:同步時脈系統 *

研究和瞭解不同時脈訊號的規範是至關重要的。表1顯示最重要的電氣參數。瞭解頻率精確度和可用的抖動十分關鍵。不同的應用必須以幾種不同的方式測量抖動,才有助於清楚地瞭解。

表1:定義頻率和輸出數量後,還有許多其他時脈參數需要考慮

與電氣參數不同,特殊情況可能會影響選擇。例如,外形和溫度範圍經常是影響產品選擇的兩個因素。

透過工具節省時間

高度整合的時脈產生器必須易於使用,許多時脈製造商都提供線上工具來協助設計人員。例如,Microchip的ClockWorks配置器和TimeFlash。ClockWorks讓購買者指定可客製的產品,接收客製資料手冊和訂購樣品。TimeFlash則是一種桌面編程工具,只需要TimeFlash2編程器和一台PC,就可以在客戶的工廠中編程「空白」可編程時脈。

當今許多智慧連網系統都從高度整合的時脈解決方案中受益良多。雖然透過多個振盪器轉換並架構集中化時脈需要仔細地規劃和佈局,但它可以降低成本、提高性能、增加功能以及提高可靠性。為您的應用程式添加高度整合的時脈比想像中更簡單吧?那麼,是時候整合您的時脈解決方案了嗎?

(參考原文:It’s time to advance your clock,by R. Colin Johnson)

訂閱EETimes Taiwan電子報

加入我們官方帳號LINE@,最新消息一手掌握!