EDA意外收穫最強成長季的秘密

2019年第一季,EDA產業營收額達到26億美元,使其成為EDA歷史上營收最為強勁的季度之一,產業高速成長的秘密是什麼?

根據電子系統設計(ESD)聯盟的資料顯示,2019年第一季EDA產業營收額達到26億美元,較去年同期增長16.3%。EDA銷售額的4個季度移動平均值(moving average,相比最近4個季度及之前的4個季度)增加了6.1%,這也讓2019年第一季成為EDA歷史上營收最為強勁的季度之一。

這一資料讓許多人跌破眼鏡,包括Mentor榮譽CEO兼ESD聯盟董事會成員Wally Rhines。他稍早前在接受《EE Times China》採訪時表示,如今不僅是幾家備受關注的系統與雲端運算大廠開始設計自家晶片,同時還有越來越多的系統設計人員也開始使用EDA工具進行系統級設計,使得購買EDA公司的數量越來越多。

人工智慧對EDA產業的影響

推動EDA產業增長的,除了系統級設計之外,人工智慧(AI)的影響也不可忽視。

「人工智慧正在為半導體產業開啟數十年以來的最佳商機,很可能成為推動半導體產業進入下一個十年增長週期的催化劑。」Mentor IC EDA執行副總裁 Joseph Sawicki援引麥肯錫諮詢(Mckinsey & Company)和普華永道(PricewaterhouseCoopers)的研究報告稱,過去無論是PC還是智慧型手機時代,機遇持續的時間並沒有這麼長久。對半導體產業來說,即便是最火熱的行動時代,也只提供了價值20%的產值。而在人工智慧時代,半導體公司將從技術堆疊(Technology Stack)上獲得50%左右的產值。

Mentor IC EDA執行副總裁 Joseph Sawicki

為人工智慧領域帶來全新發展機遇的要素,一方面源自車聯網、智慧城市、物聯網及工業物聯網等領域,正在將生成的海量資料源源不斷的傳送到雲端,這一趨勢極大改變了現有的資料中心架構;除了資料中心聚合之外,另一重要趨勢是大量的機器學習及人工智慧設備和運算被部署在邊緣側,以加速資料處理及回應過程。資料顯示,2016~2021年,邊緣運算年複合成長率將高達190%,增速顯著超越雲端。

資本的走向也驗證了這一趨勢。如下圖所示,2012~2019年的7年間,風險投資機構的資金走向主要集中在機器學習和人工智慧領域,共獲得19.06億美元,其次為加密貨幣5.09億美元,高速通訊/5G 4.77億美元。

Alphabet董事長John Hennessy曾提出,摩爾定律的終結,以及更高速通用運算的到來,標示著新的黃金時代已開啟。因此,無論是以軟體為中心,還是以硬體為中心的傳統思想都存在局限,特定域語言和架構則更有希望。

Sawicki對此表示贊同,並認為特定域(domain-specific)架構將是實現下一波增長的關鍵動力。他列舉了一些特定領域的人工智慧/深度學習控制器,其中,45款針對視覺/臉部辨識;38款鎖定資料中心/雲端人工智慧/HPC;36款針對邊緣運算;26款自動/輔助駕駛;14款深度學習訓練,分列1~5位。值得一提的是,儘管GPU目前仍然是IC收入中最大的部分,但ASIC晶片的市場增速最快。

連接人工智慧與和晶片設計橋樑

一直以來,SoC晶片的設計方法學都是在RTL基礎上進行驗證。「但在人工智慧時代,人工智慧/機器學習IP和IC設計在架構最佳化、功耗預算、晶片容量和高速I/O方面都面臨許多挑戰,IC設計師需要新的設計方法和工具,所以我鼓勵他們採用高階綜合(High-Level Synthesis;HLS)進行更多探索。」之所以這樣表態,Sawicki表示是因為在人工智慧時代,演算法開發平台的設計語言是C或者C++等語言,為了實現統一原生的設計環境,最好使用同樣的晶片開發環境。

Sawicki把HLS比喻為「連接人工智慧原生環境和晶片設計的橋樑」,可以借此協助客戶更好地設計架構、管理記憶體分配和神經網路的寬度與縱深,以及決定在晶片內部放置多少流水線等,只有管理好這些要素,才能為垂直應用提供經過最佳化的IC軟體體驗。

而一旦設計方法論發生轉變,那麼驗證方法學也需要隨之改變。傳統IC的驗證方法就是測試規則、架構和規範,而在人工智慧時代,面臨更多的是垂直應用,驗證通常發生在應用層面。這就需要透過相關技術模擬出一個虛擬人工智慧引擎,然後把演算法資料推送到硬體模擬系統中的人工智慧引擎上去執行程式碼處理和最終應用,以便獲得整體的性能、功耗及資料。這樣,在晶片尚未開發之時就能及早掌握整個系統的性能表現。

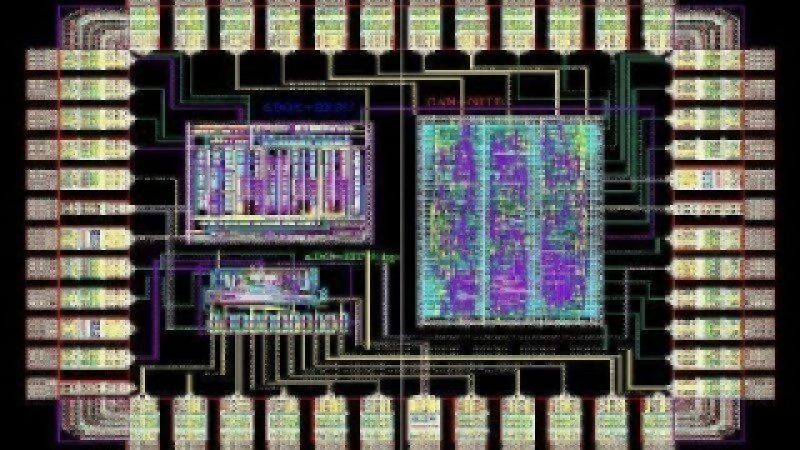

包括C/C++/System C HLS、HLS驗證,以及低功耗HLS三大產品線在內的Catapult HLS工具箱是Mentor針對HLS方法學推出的新產品。在之前的採訪中Mentor就曾表示,人工智慧/機器學習需要進入下一步抽象和功耗分析,HLS結果並不比手動編寫的RTL差,甚至更強,時間更快(能夠縮短4倍)。此外,HLS易於重映射多種技術,例如可以針對各種技術重映射相同C程式碼,輕鬆切換製程,快速探索可行的替代技術並確定最佳實現。而根據Nvidia的回饋,在採用Catapult HLS工具後,Tegra X1晶片的驗證效率提高了50%,驗證成本降低了80%。

考慮到將人工智慧導入EDA已是大勢所趨,目前,無論是在Pattern分析還是深度資料分析中,Mentor正在廣泛利用人工智慧和機器學習,加速新產品和新技術的開發。比如Machine Learning OPC可以將光學鄰近效應修正(OPC)輸出預測精度提升到奈米級,同時將執行時間縮短3倍。而在此之前,完成同樣的工作量,需要4,000個CPU 不間斷地運行24小時;而在LFD中,透過機器學習既解決了海量未標記資料的提取,同時也利用訓練好的資料使預測更加精準。結果顯示,與基於全晶片模型的模擬相比,在保持最佳精準度的同時還使性能提高了10~20倍。

而在深度資料分析上,除了來自Solido的variation aware的設計外,採用RCD(root cause deconvolution)技術消除診斷結果雜訊,減少根因分析時間,發現其他隱藏較深導致良率問題的根源,也是非常典型的人工智慧在EDA工具中的應用。

下圖來自名為PAVE 360新方案的一個執行結果。透過Mentor人工智慧引擎讓自動駕駛車輛在虛擬環境中進行駕駛,然後將虛擬資料與左圖中西門子駕駛安全輔助設計測試軟體Simcenter Prescan和右圖中西門子機電一體化系統模擬平台Simcentor Amesim連接,透過互動實現電子系統和機械系統一體化的模擬驗證過程。

這套系統對晶片廠商、OEM和Tier one廠商,以及整車廠而言都是極具價值。這意味著驗證測試人員不再需要開幾千公里去驗證車輛的動力傳動、底盤、乃至真實的道路環境,所有的一切在晶片、車輛、道路建成之前就會得到精確預測,極大提升了設計和製造的效率。

這一案例就是數位雙胞胎(Digital Twin)技術的真正實現。其實西門子在併購Mentor之後,「還收購了很多與EDA相關的企業」,包括針對低頻設備的電磁和熱分析軟體發展商Infolytica、加強IC測試的方案提供商Sarokal、基於機器學習和變數認知設計特徵軟體發展商Solido、線束線纜分析設計公司Comsa,以及針對IC硬體隨機故障檢測的安全分析/自動校正和模擬工具開發商Austemper,用以加強Mentor在EDA 4.0設計和驗證工具的功能和性能。

「EDA 4.0」是Mentor中國區總經理凌琳在ASPENCORE舉辦的「2019年中國IC領袖峰會」上首次提出的概念。與之相對應的是,在EDA 1.0時代,基本都還是最原始的閘級電路設計方法學;而到了EDA 2.0時代,開始引入RTL設計方法學,包括Cadence、Synopsys等公司相繼誕生;在EDA 3.0時代,設計輸入進一步提高了抽象層次,導入了基於IP複用的SoC設計方法學,一些EDA公司開始併購IP廠商,同時Arm等獨立IP廠商迅速壯大。

隨著自動駕駛、物聯網、雲端運算平台和智慧家居等應用場景都需要從IC到系統的完整方案,而特定域架構的人工智慧加速晶片可以滿足定制化要求。傳統的EDA閘級、RTL甚至IP級設計都無法滿足這種晶片設計的綜合、模擬和驗證要求。Mentor因此提出了EDA 4.0的概念,即透過3D IC和SiP等新的晶片製造技術、ECAD/MCAD協同設計,以及虛擬/物理數位雙胞胎系統設計等來實現人工智慧系統、巨量資料分析和雲端運算應用。

本文為姊妹刊國際電子商情原創文章

訂閱EETimes Taiwan電子報

加入我們官方帳號LINE@,最新消息一手掌握!